-

[IT | 기술] (디일렉) 반도체 하이브리드 본딩 기술이 뜬다2023.07.25 PM 05:13

본딩(Bonding)은 무엇인가를 붙인다는 의미입니다.

반도체 패키지 분야에선 칩 다이(die)와 패키지 기판(substrate)을 붙일 때 ‘본딩한다’는 말을 씁니다. 붙일 때는 칩 다이와 기판에 전기(데이터)가 통하는 경로를 만들어줘야 합니다. 과거 데이터 입출력(IO, -nput/Output)이 많지 않았을 때 주류는 금선을 활용하는 와이어 본딩(wire bonding) 방식이었습니다. 물론 지금도 일반 칩은 금선으로 본딩을 많이 하긴 합니다.

연산량이 높고 데이터 IO가 많은 칩의 경우라면 플립칩-볼그리드어레이(FC-BGA:Flip Chip Ball Grid Array) 패키지 방식을 주로 씁니다. 플립칩 볼그리드어레이는 용어 그대로 칩 다이와 패키지 기판 사이에 솔더볼(solder ball)을 격자(grid) 형태로 배치(array)해 붙이는 방식입니다. 솔더볼은 칩 다이가 패키지 기판과 맞닿기 때문에 범프(bump)라고도 불립니다. FC-BGA 패키지 방식은 우리가 흔히 볼 수 있는 중앙처리장치(CPU), 시스템온칩(SoC), 그래픽처리장치(GPU) 등에 활용됩니다.

연산량이 높아지면서 솔더볼 범프 방식으론 대응이 안 되는 칩도 생겨나기 시작했습니다. 솔더볼 범프간 간격(pitch)은 일반적으로 150마이크로미터(㎛) 수준입니다. 제곱밀리미터(㎟)당 50개 IO를 배치할 수 있습니다. 이 간격을 더 줄이기 위해 개발된 것이 구리(Cu) 소재 기둥(Pillar)을 세우고 그 위로 범프를 배치하는 기술입니다. 패키지 업계 관계자들이 얘기하는 “카파 필러 범프 배치가 어쩌고 저쩌고”할 때 바로 그 기술입니다. 구리 기둥 범프 기술을 활용하면 범프간 간격은 통상 50㎛로 줄어듭니다. ㎟당 400개 IO를 배치할 수 있습니다. 여기서 한 단계 더 발전한 기술은 구리 마이크로(μ)기둥 범프입니다. 범프 간격이 20㎛로 줄고 ㎟당 2500개의 IO를 만들 수 있습니다. 최신 고속 반도체 칩은 구리 μ기둥 범프 기술을 활용해 만든다고 보면 됩니다.

범프의 진화는 붙이는 방법에도 차이를 만들어냈습니다. 일반 솔더볼 범프 방식은 일종의 오븐 장비를 활용, 열로 칩 다이와 기판을 붙이는 방식을 썼습니다. 업계에선 이 공정을 매스 리플로(MR:Mass Reflow)라고 부르고 있습니다. MR 방식은 칩 다이를 얹은 기판 등을 벨트에 올려놓으면 이 벨트가 움직이면서 순차로 열을 받게 하는 구조입니다.

그러나 구리 기둥 범프 혹은 이보다 더 미세한 구리 μ기둥 범프를 활용하는 칩의 경우 패키지 기판 두께도 얇아지게 됩니다. 일반 MR 방식으로 열을 가하면 기판의 휘어짐(warpage) 문제가 발생하는데, 이 과정에서 접합이 제대로 되지 않는 등 다양한 문제가 발생합니다. 이 때문에 열(thermal)과 누르는 압착력(compression)을 동시에 활용하는 TC(Thermal Compression) 본딩 방식이 생겨났습니다. 최근에는 이 마저도 어려우니 레이저로 1~2초 가량 칩에 국부적으로 열을 가해 칩 다이와 기판을 붙이는 LAB(Laser Assisted Bonder) 방식도 개발돼 양산 라인에 적용이 이뤄지고 있습니다.

패키지 본딩 공정의 궁극적 진화 기술은 범프를 만들지 않고 구리(Cu)와 구리를 바로 맞닿게 만드는 것입니다. 업계에선 Cu to Cu 본딩이나 다이렉트 본딩, 혹은 하이브리드 본딩 등의 기술명으로 불립니다. TSMC는 이 기술을 자체적으로 CoWoS(Chip on Wafer on Substrate), 인텔은 포베로스 다이렉트라 부릅니다.

하이브리드 본딩은 가공된 웨이퍼 위로 이종(異種) 칩 다이를 곧바로 올려서 붙이기 때문에 더 이상 ‘후공정’이라 부를 수 없는 전공정의 영역이 됩니다. 붙이기 전에 화학기계적연마(CMP, Chemical Mechenical Polishing) 공정을 진행해 평탄화를 해야 하고, 칩을 아주 정확하게 올려야 하며, 올린 뒤에는 진공 상태에서 플라즈마를 활용해 공유결합(共有結合, covalent bond)을 이뤄내야 합니다. 공유결합은 원자가 전자쌍을 공유하며 만드는 화학적 결합을 의미합니다. 하이브리드 본딩이 이뤄지면 해당 칩에는 언더필이나 접착재나 필름 사용이 없거나, 줄어들게 되니까 희비가 갈리는 관련 기업도 꽤나 있을 것으로 관측이 되고 있습니다.

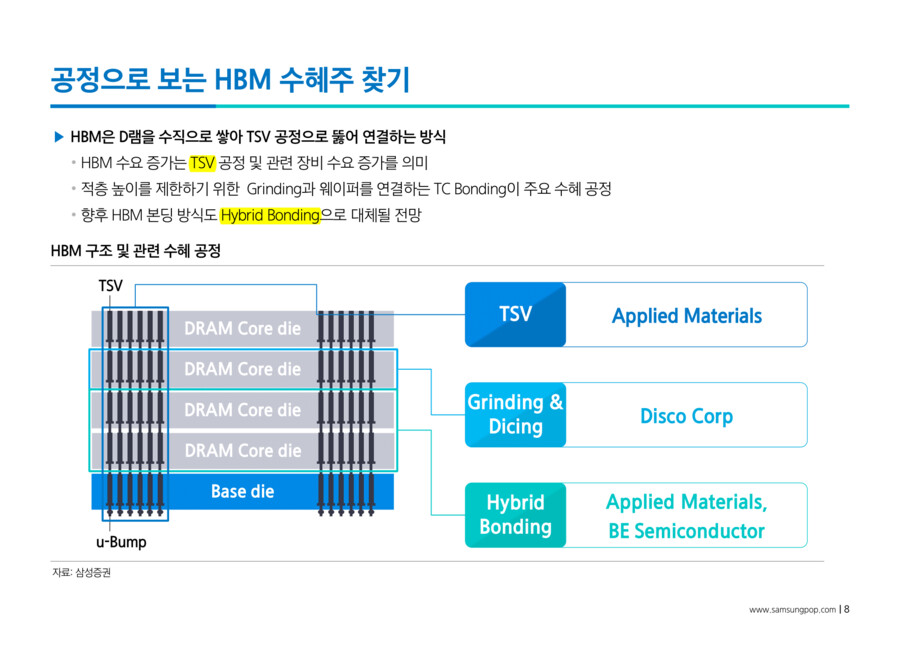

3D V캐시 명칭(X3D)이 붙은 AMD 신규 CPU 라이젠 시리즈가 TSMC의 하이브리드 본딩 공정 결과물입니다. L3 캐시를 별도 칩으로 만들어서 CPU 위로 붙였고, 이를 통해 용량 및 전력 성능 효율성을 높인 것으로 평가받고 있지요. 인텔도 양산을 서두르고 있습니다. 메모리 업계는 고대역폭메모리(HBM)의 단수가 계속 높아질 경우 하이브리드 본딩 기술을 접목한다는 계획을 세운 것으로 알려지고 있습니다.

범프를 사용하지 않기 때문에 높이를 줄일 수 있습니다. 삼성전자의 경우 D램 4F스퀘어 기술 개발 후 하이브리드 본딩 기술로 집적도를 높인다는 전략을 세운 것으로 전해집니다. 정부도 이러한 어드밴스드 패키지 공정 생태계 개발을 위해 예타 사업을 준비 중입니다. 미리 알아야 예타가 통과됐을 때 기술 개발 과제도 따낼 수 있을 것으로 보입니다. 기술 경쟁력과 시장 상황은 기업의 주가에도 큰 영향을 미칩니다. 투자업계도 이 분야에 많은 관심을 쏟고 있습니다. 근래 네덜란드 베시라는 기업은 하이브리드 본딩 장비로 주가를 크게 올리고 있지요.

전자부품 전문미디어 《디일렉》은 오는 7월 하이브리드 본딩과 관련한 생태계 전반과 기술 도전 과제를 소개하는 콘퍼런스를 개최합니다.

많은 관심을 부탁드리겠습니다.

user error : Error. B.