[서울경제]

정보기술(IT) 시장에 관심 많으신 독자 여러분 안녕하세요. 요즘 우리 나라 반도체 업계에서 고대역폭메모리(HBM) 빼면 이야기가 안되죠.

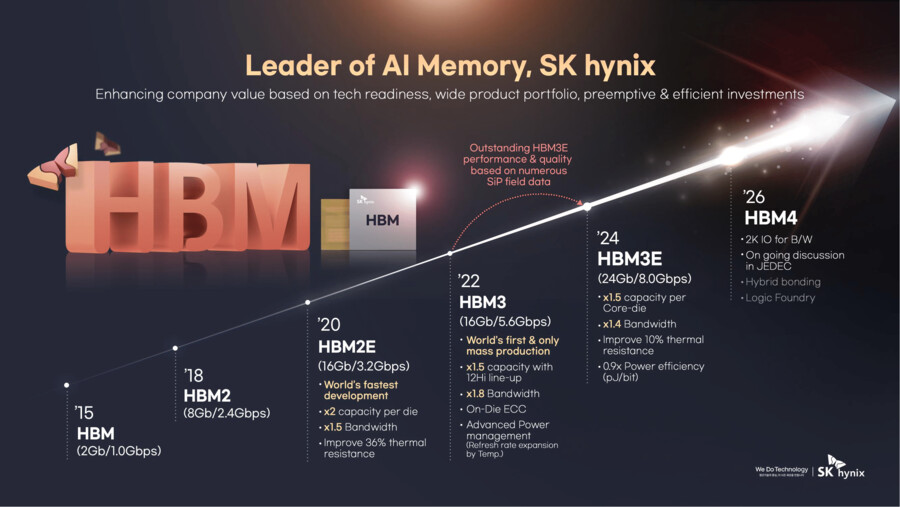

내년에는 지금 나오는 HBM3보다 기능이 더 업그레이드 된 HBM3E가 출시된다고 하는데, 이제 슬슬 다음 작품인 HBM4의 스펙이 궁금해지기 시작합니다. 과연 HBM4는 언제, 어떻게 무슨 모양으로 나올까. 그런데 말입니다. 몇 달 전 SK하이닉스가 살짝 힌트를 줬습니다. 애널리스트와 주주들을 상대로 개최한 테크 세미나에서 HBM의 미래 비전을 소개한 적이 있어서인데요.

SK하이닉스가 소개한 장표 몇 가지를 보면서 HBM4에서 달라지는 3가지 모습에 대해 짚어보겠습니다. 내용들을 보시기 전에 제가 지난 4월에 작성했던 'SK하이닉스가 HBM에 진심인 이유' 편을 훑어보신다면 훨씬 더 유익한 내용이 될 것 같습니다. 입출구(I/O) 수부터 시작하겠습니다.

1. 2048개의 I/O

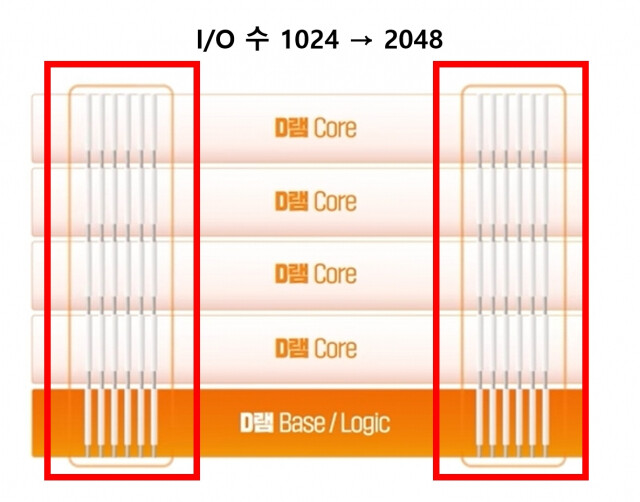

I/O는 HBM 콘셉트에서 상당히 중요합니다. I/O 수는 D램에 정보가 들어오고 나가는 통로를 말하죠. D램이 얼마나 빠르게 데이터를 전송하는가를 알 수 있는 ‘대역폭’을 결정하는 중요한 요소이기도 합니다. 삼성전자·SK하이닉스·마이크론 테크놀로지 등 HBM을 생산하는 업체들은 여러 개의 D램을 쌓은 뒤 수직으로 뚫는 실리콘관통전극(TSV) 기술로, 데이터가 마치 엘리베이터처럼 위 아래로 이동하는 1024개의 I/O를 HBM에 구현했습니다.

2026년 HBM4 양산 계획을 밝힌 SK하이닉스. SK하이닉스가 대역폭 확장을 위한 2K(2000개) 이상의 IO를 적용하겠다고 설명했습니다. 또한 HBM4 규격에 대한 JEDEC 협의가 막바지에 달한 것으로 알려집니다. 자료출처=SK하이닉스

통상 그래픽처리장치(GPU) 옆에 장착되는 GDDR 칩의 I/O 수는 32개였는데요. HBM은 이것의 32배인 1024개를 뚫으면서 대역폭 확장을 이뤄냈죠. 이 1024개의 I/O 수가요. HBM4를 양산할 무렵인 2026년에는 2000개 이상으로 늘어나는 것이 검토된다고 합니다. 최근 업계에서 나오는 구체적인 I/O 스펙은 2048개로 알려지는데요. 딱 2배가 늘어나는 것이죠. 동일한 호텔 속의 1024개 초고속 엘리베이터가 2048개까지 증가한다는 이야기입니다.

HBM 안에서 정보들이 드나드는 1024개의 엘리베이터가 3년 뒤에는 2048개까지 늘어나는 HBM 규격이 채택될 것으로 보입니다. 이것을 먼저 구현하기 위한 삼성전자, SK하이닉스, 마이크론 테크놀로지 등 D램 메이커 간 경쟁이 치열해질 것으로 예상됩니다.

HBM4와 I/O 수 증가에 관한 건은 반도체 규격을 정하는 단체인 국제반도체표준협의기구(JEDEC)에서 최종 검토 중이고 이제 막바지에 다다랐다고 합니다. 이 스펙이 완전히 확정되면 HBM 제조사들이 더욱 활발하게 I/O 기술 선점에 나설 것으로 보입니다.

HBM을 호텔 엘리베이터에 한번 더 비유해보려고 하는데요. 1024개의 호텔 엘리베이터가 있는 같은 면적에 2000개가 넘는 엘리베이터를 장착하는 것을 설계하려면 우선 엘리베이터 사이 공간이 좁아져야 할 것입니다. 이 공간을 '피치(pitch)'라고도 하죠. 현재 HBM3에서 이 I/O 간 거리는 25~30마이크로미터(㎛·100만분의 1m), 그러니까 사람 머리카락 지름의 4분의 1 크기인 0.025㎜ 정도로 알려져 있습니다.

산술적으로 보면 구멍 사이 25㎛ 피치를 절반 수준으로 줄이거나 TSV 지름을 더 얇게 만드는 방법이 활발하게 연구될 것으로 보입니다. I/O 구멍인 실리콘관통전극(TSV)을 뚫는 데 쓰이는 식각(에칭) 장비는 이 분야 강자 미국 램리서치가 공급하는 것으로 알려져 있습니다. 과연 삼성전자, SK하이닉스가 식각 업체들과 어떤 협업을 해서 누가 더 빨리 2000개 이상의 I/O수를 구현해낼 지 관심을 가지고 지켜봐야겠습니다.

2. 하이브리드 본딩

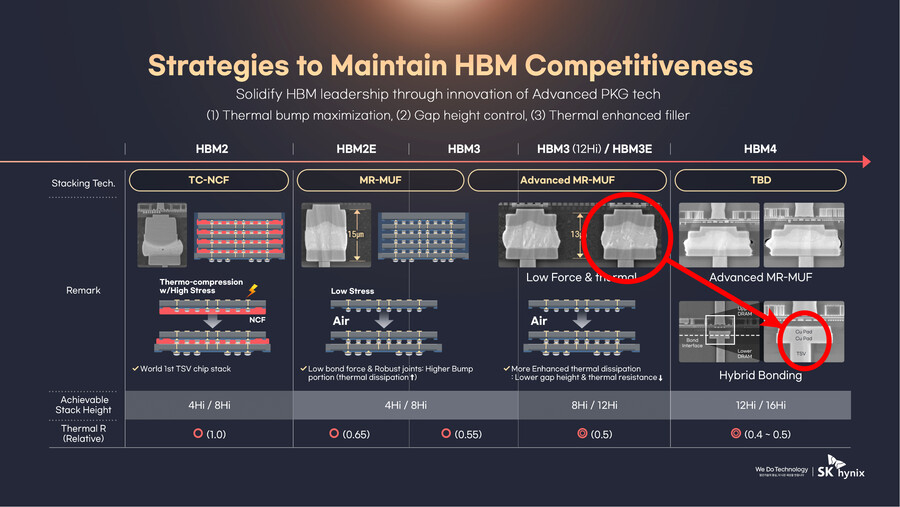

SK하이닉스는 13마이크로미터 간격으로 칩을 쌓는 기술을 개발했죠. 하이브리드 본딩이 구현되면 배선과 배선, 칩과 칩을 아예 포개어버리는 것을 구현할 수 있기 때문에 HBM의 두께를 상당히 혁신적으로 줄일 수 있습니다.

SK하이닉스 테크 세미나의 장표를 자세히 보시면 '하이브리드 본딩'이라는 용어도 심심찮게 나옵니다. 지금은 칩과 칩 사이를 '범프'라는 것으로 연결하죠. 범프는 칩 간 가교 역할을 합니다. 하이브리드 본딩은 아예 이 가교를 없애고 포개어버린다는 콘셉트입니다. SK하이닉스 관계자는 “HBM4에서는 MR-MUF와 하이브리드 본딩을 ‘투트랙’으로 개발할 예정”이라며 “각 기술의 특장점이 시장에서 선택될 것”이라고 귀띔했습니다.

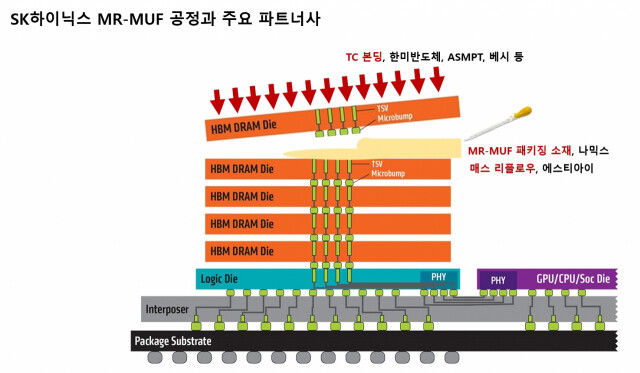

기존 MR-MUF 공정에서 활용됐던 TC 본딩, 매스리플로우, MR-MUF용 패키징 소재 등이 하이브리드 본딩 시장에서는 어떤 방식으로 생존할 것인지 살펴보는 것도 포인트입니다. 사진제공=AMD

하이브리드 본딩을 구체적으로 이야기하기 전에 현재 SK하이닉스가 구현하는 HBM 공정을 설명드리면요. 현재 SK하이닉스는 칩 간 결합을 위해 매스리플로우 몰디드 언더필(MR-MUF) 공정을 쓰죠. MR-MUF는 우선 D램 칩을 마치 초벌구이처럼 차례차례 쌓아 붙이고 난 뒤에요. 오염과 열로부터 보호해줄 수 있는 끈적한 액체를 범프 사이와 칩 전반에 주입하고(Molded Underfill)→ 칩을 한증막같은 곳에 넣어 굳히는(Mass reflow) 방식을 씁니다.

하이브리드 본딩은 범프가 없으니까 이 과정이 없습니다. 배선 역할을 할 곳에 구멍을 뚫어서 구리(Cu)를 집어넣고요. 마치 샌드위치처럼 이걸 딱 포개어버립니다. 파운드리 1위 업체 TSMC가 SoIC라는 기술로 이 하이브리드 본딩을 가장 먼저 구현하기도 했죠.

SK하이닉스에 따르면 현재 MR-MUF로 HBM 칩 사이 간격을 13㎛까지 줄인 상황인데요. 하이브리드 본딩을 구현하면 이 13㎛ 미세 간격마저 없어지는 것은 물론이고 범프라는 가교이자 '장애물'이 없어지면서 데이터 이동 속도도 훨씬 빨라질 수 있습니다.

하이브리드 본딩의 난도는 쉬워보이지만 상당히 높습니다. 배선 역할을 할 구리(금속)의 열팽창을 기다리며 칩과 칩(또는 웨이퍼와 웨이퍼) 간 결합을 유도하면서, 바로 옆의 절연체 역할을 하는 산화막(SiO₂)까지 동시에 붙여야 하고요. 발열 최소화를 위해 심어놓은 수 만개의 더미 범프 역할을 할 새로운 구멍들까지 정교하게 붙여야 하는 방법을 개발해 내야 합니다. 난도가 어려운 만큼 증가하는 공정 시간과 수율, 생산 단가도 고려해야겠죠.

현재 양산 중인 SK하이닉스 HBM3의 경우 마치 '초벌구이' 콘셉트처럼 칩과 칩을 쌓아올려서 압착해 연결하는 열압착(TC) 본더 장비를 한미반도체(042700), ASMPT 등이 공급합니다. 리플로우 장비는 국내 에스티아이(039440), MUF 공정을 위한 액체 소재는 나믹스가 생산하는 것으로 알려져있죠.

HBM에서 하이브리드 본딩이 가시화한다면 이 장비 생태계도 상당한 변화가 있을 듯 합니다. SK하이닉스의 하이브리드 본딩 구현을 위해 다양한 업체들이 도전장을 내밀거나 후보로 떠오르고 있는 것으로 알려져 있는데요. SK하이닉스와 본딩 분야에서 협력한 적 있는 한화정밀기계, 과거 하이브리드 본딩 개발을 진행한 적이 있었던 한미반도체가 장비 국산화의 후보로 떠오르고 있습니다.

이들이 SK하이닉스의 양산 목표 시점인 2026년까지 혁신적인 장비를 개발해낸다면 그야말로 '대박'이 나는 거겠죠. 현재 이 분야의 글로벌 최강자는 네덜란드 베시와 미국 어플라이드 머티어리얼즈입니다. 장비 업계에서 빵빵한 영향력을 가진 두 회사는 아예 손을 잡고 지난 2020년부터 싱가포르에서 하이브리드 본더 기술 고도화와 양산에 주력하고 있죠. 과연 SK하이닉스가 하이브리드 본딩이 임박한 시점에 결국 이들과 협력하게 될지, 한국에서 새로운 파트너를 찾게 돼 미리 장비 회사 주식을 구매해뒀던 투자자들에게 큰 기쁨을 줄지 주목해봐야 할 부분입니다.

3.16단

12단에서 16단으로 바뀌더라도, 부피는 전작과 비슷해야 경쟁력이 생기기 때문에 때문에 칩 뒷면을 잘 갈아서 쌓는 것이 숙제입니다. 사진제공=AMD

HBM4는 높이도 달라집니다. 지금까지는 12단의 HBM이 쓰였는데 4단 더 높이 쌓인다는 뜻인데요. 지금까지 SK하이닉스는 10나노 3세대, 그러니까 1z D램을 활용해 HBM을 12층으로 쌓아 만드는 것으로 알려졌습니다. 이게 4단 더 높아진다는 얘기죠.

그런데 그냥 4단 더 쌓는다면 정말 수월하겠지만 반도체 업계의 숙명은 '축소'입니다. 까다로운 고객사들의 요건을 만족하려면 16단을 쌓으면서도 양산 중인 HBM3와 높이가 거의 같게 만들어서 경쟁력을 쌓아야 한다는 얘기입니다. 예를 들어 세계 최대 AI 반도체 업체 엔비디아가 요구하는 HBM의 두께는 약 720㎛ 정도로 알려졌다. 만약 12단으로 쌓는다면 한 칩 당 60㎛의 공간이, 16단으로 쌓게 되면 기존보다 25% 감소한 45㎛ 공간이 주어진다는 이야기인데요. 이렇게 축소를 하려면 D램의 뒷면을 최대한 갈아내면서도 얼마나 고성능을 유지할 것인가가 관건으로 보여집니다. 또한 2번 카테고리에서 말씀드린 범프가 없어지는 하이브리드 본딩 공정의 필요성도 더욱 증가하게 되는거죠.

HBM의 구조에 대한 이야기를 했으니 마지막으로 미래 HBM의 활용도에 대해서도 이야기를 해봐야 할 것 같습니다. 바로 HBM의 위치인데요.

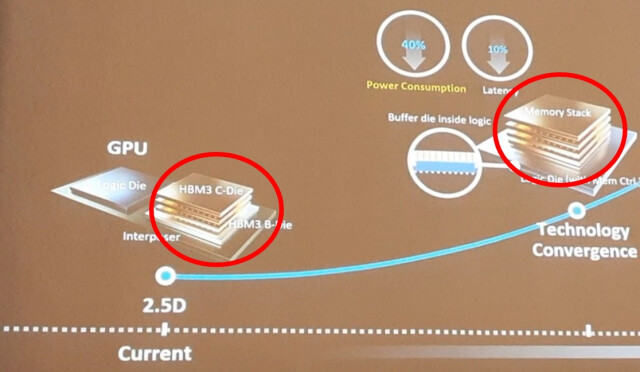

CPU와 조화를 이룬 HBM의 위치 변화를 잘 살펴보면요. 현재 로직 반도체 바로 옆에서 2.5D 패키징된 HBM이 앞으로 로직 반도체 위로 올라갈 수도 있습니다. 이때 전력효율과 지연성이 각각 40%, 10%씩 개선된다는 건데요. 칩이 포개지면서 생기는 발열 이슈도 잘 잡아내야할 것이라는 관측이 나옵니다. 자료출처=삼성전자

통상 지금까지는 HBM이 GPU 바로 옆에 붙어서 움직이는 경우가 많았는데, 삼성전자 등 칩 메이커들이 최근 다양한 학회에서 HBM이 로직 다이 바로 위에 올라가 마치 한 칩처럼 움직일 수 있다는 가능성을 제시했습니다. 3D 패키징된 칩을 또 3D 패키징하는 셈이죠. 삼성전자는 이렇게 하면 기존보다 전력 효율이 40%, 데이터 지연성이 10% 향상될 수 있다는 가능성도 제시했습니다. 이 경우 포개어진 칩 사이에 발생하는 발열 이슈를 어떻게 잡을지가 관건입니다.

고객사들이 원하는 위치에 HBM이 놓이게 되면 단순한 D램 모듈용 제품을 생산하던 칩 메이커들이 ‘커스텀(맞춤형) D램’ 시장에 보다 적극적으로 뛰어들 가능성이 더욱 커집니다. 패키징 시장 성장으로 인한 메모리 시장의 판도 변화도 상당히 중요해졌습니다. ‘메모리의 파운드리화’가 괜히 중요한 부분이 아닙니다.

이렇게 다가올 HBM4 시대의 키 포인트 3가지를 살펴봤는데요. 앞으로 어떤 변수가 나올 지 모르는 HBM 시대. 아직 전체 D램 시장에서의 규모는 크지 않지만 삼성전자, SK하이닉스, 미국 마이크론 등 굴지의 D램 회사들이 열띤 투자 및 첨단 기술 경쟁을 벌이는 만큼 변화를 주의깊게 살펴봐야합니다. 남은 추석 연휴 잘 마무리하세요!